A Modern Electronics Manufacturing Process

PROCESS OVERVIEW

How the Nano OPS Process Works

Nano OPS uses an advanced electronics manufacturing process based on directed, layer-by-layer additive fabrication. This streamlined approach replaces thousands of traditional steps with a unified additive manufacturing process, enabling rapid development, consistent wafer-scale output, and end-to-end control.

1. Concept & Design

Initial electronics or packaging concepts are defined and translated into printable designs.

2. Rapid Prototyping

Functional components and structures are fabricated directly on the wafer, enabling fast design iteration.

3. Test & Validate

Printed devices are characterized evaluated according to specifications.

.png)

4. Iterate & Refine

Design changes are implemented quickly without retooling or process redesign.

Pilot-Scale Manufacturing

Wafer-scale production validates repeatability, precision, and manufacturability.

Digital Design Input & Wafer Preparation

The process begins with device or advanced packaging designs defined digitally through standard GDS files. These designs are loaded directly into the Nano OPS system, enabling immediate translation from concept to nanoscale structures without additional tooling. Wafers are prepared and positioned for processing, forming the foundation for fully integrated additive fabrication. This digital-to-wafer workflow reduces front-end complexity and primes the system for precise, reproducible manufacturing.

Directed-Assembly Additive Fabrication

At the core of our additive manufacturing process is directed-assembly printing, which builds passive and active components directly onto the wafer. Interconnects, traces, RF structures, and thermal features are printed only where required, producing tightly controlled nanoscale geometry at high throughput. Automated process control ensures consistent performance and scalability across each layer. This method eliminates the rigid sequencing, masks, and material limits associated with traditional lithography-driven workflows.

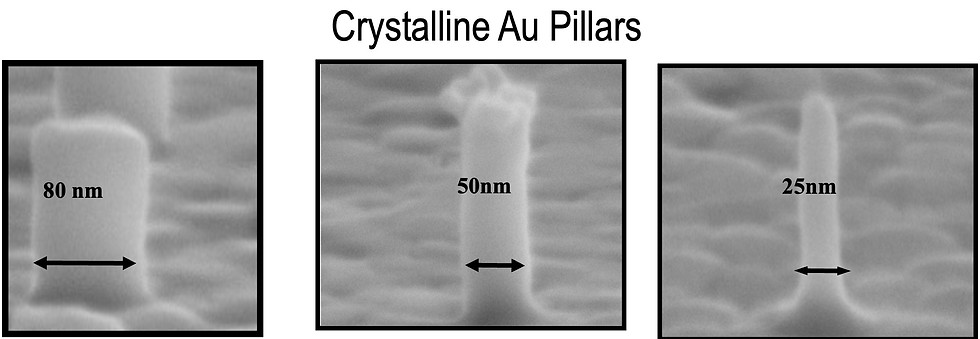

Electrophoretic Directed Assembly - EPx Platform

ACS Nano, 8 (5), 2014.

All assembled Nanoparticles are completely fused insitu.

Interconnects Properties

-

Directly assembled structures properties are equivalent to electroplating, CVD and PVD fabrication.

-

Directly assembled metallic structures (Cu, Ag, Al, Au, and W, etc.) in addition to semiconductors and dielectrics were demonstrated.

-

Resistance of assembled interconnects is the same as bulk (electroplated interconnects).

-

TEM shows that NPs completely fuse without any voids at room temperature.

-

Nanopillars have polycrystalline nature.

Fast Fluidic Assembly Process - FFx Platform

Impact

Adv. Packaging On Demand

Nano and Micro-electronics

On Demand

Fast Prototyping

and Development Cycle

Security

Sustainable

Material Innovation

20 nm Feature Precision

Our nanoscale printing process achieves feature sizes as small as 20 nm, enabling device structures far beyond the limits of traditional lithography or inkjet-based techniques. This level of nanofabrication precision is essential for next-generation semiconductor devices, flexible displays, and high-performance microsensors. By reducing reliance on subtractive patterning, teams gain more design freedom, tighter geometries, and consistent nanoscale definition across the wafer.

1000x Faster Manufacturing Cycles

The platform prints conductive, semiconducting, and insulating materials up to 1000× faster than inkjet or 3D printing approaches. This acceleration dramatically shortens iteration cycles, allowing engineers to validate and refine device designs at unprecedented speed. By eliminating thousands of steps in the traditional semiconductor workflow, our nanoscale printing method reduces delay, minimizes process bottlenecks, and supports continuous development from concept through pilot production.